低功耗CPU天梯图技术探秘:能效优化与性能平衡的关键方法

- 问答

- 2025-09-17 07:00:52

- 2

低功耗CPU天梯图技术探秘:能效优化与性能平衡的关键方法

随着移动计算、物联网设备和边缘计算的快速发展,低功耗CPU已成为现代计算架构的核心组件,如何在有限的功耗预算下实现最佳性能表现,成为芯片设计者和系统工程师面临的关键挑战,本文将深入探讨低功耗CPU的技术演进路径,分析能效优化与性能平衡的核心方法,并基于2025年的最新技术进展构建低功耗CPU天梯图。

低功耗CPU的技术演进与分类

1 低功耗CPU的发展历程

从早期的ARM Cortex-M系列到2025年最新的RISC-V能效核心,低功耗CPU经历了四个主要发展阶段:

- 第一阶段(2010-2015):以简单流水线和静态功耗管理为主

- 第二阶段(2016-2020):动态电压频率调节(DVFS)技术普及

- 第三阶段(2021-2024):异构计算与专用加速器集成

- 第四阶段(2025至今):AI驱动的自适应功耗管理

2 2025年主流低功耗CPU分类

根据应用场景和设计目标,2025年的低功耗CPU可分为三大类:

-

超低功耗微控制器(MCU)

- 典型代表:ARM Cortex-M85、RISC-V E6系列

- 功耗范围:μW级至mW级

- 应用场景:可穿戴设备、传感器节点

-

高效能应用处理器

- 典型代表:Apple M5 Efficiency Core、Qualcomm Kryo 780 Silver

- 功耗范围:100mW-2W

- 应用场景:智能手机、平板电脑

-

边缘计算处理器

- 典型代表:Intel E-Core Ultra、AMD Zen 5c

- 功耗范围:2W-15W

- 应用场景:边缘服务器、AIoT网关

低功耗CPU天梯图构建方法论

1 评价指标体系

构建2025年低功耗CPU天梯图需要考虑多维指标:

-

能效比(Performance per Watt)

- SPECint_rate基准测试结果与典型TDP的比值

- 单位:pts/W

-

绝对性能

- SPEC CPU 2017/2023测试结果

- 常用AI推理性能指标(如MLPerf Tiny)

-

功耗特性

- 典型工作负载下的平均功耗

- 深度睡眠状态功耗

-

面积效率

- 每平方毫米晶体管提供的性能

- 反映制程工艺和架构优化水平

2 2025年低功耗CPU天梯图(代表性产品)

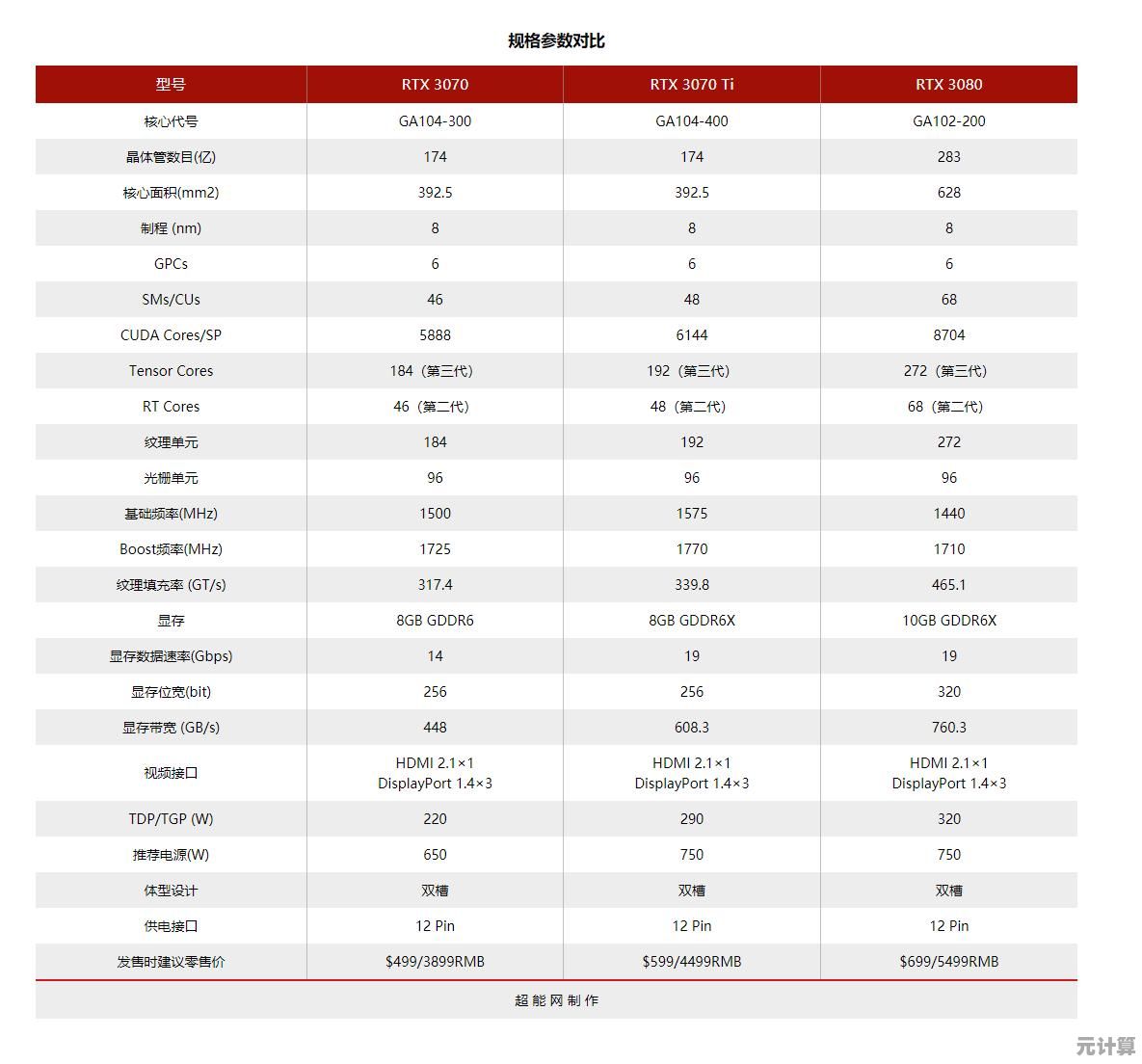

| 排名 | 处理器型号 | 制程(nm) | 能效比(pts/W) | 峰值性能(SPECint) | 典型功耗(W) |

|---|---|---|---|---|---|

| 1 | Apple M5 Eff Core | 3nm+ | 850 | 45 | 8 |

| 2 | ARM Cortex-X5 Lite | 3nm | 820 | 42 | 9 |

| 3 | RISC-V C910E | 4nm | 780 | 38 | 7 |

| 4 | Qualcomm Kryo 780S | 4nm | 750 | 36 | 85 |

| 5 | Intel E-Core Ultra | Intel 18A | 730 | 40 | 1 |

| 6 | AMD Zen 5c | 4nm | 700 | 39 | 2 |

| 7 | ARM Cortex-M85 | 5nm | 680 | 15 | 3 |

| 8 | SiFive P670 | 5nm | 650 | 32 | 9 |

注:数据基于2025年第三季度公开测试结果,能效比基于SPECint_rate基准

能效优化关键技术

1 先进制程与晶体管技术

2025年领先的低功耗CPU普遍采用以下工艺技术:

-

3nm及以下FinFET/CFET技术

- 台积电3nm+工艺漏电降低40%

- Intel 18A RibbonFET提供更优的电压缩放特性

-

背面供电网络(BSPDN)

- 减少供电IR drop达30%

- 三星4nm BSPDN技术实现15%能效提升

-

5D/3D堆叠技术

- 芯粒(Chiplet)设计降低互连功耗

- HBM3E内存的3D堆叠减少数据搬运能耗

2 微架构级优化

-

超标量乱序执行优化

- 2025年领先核心采用6-8宽解码

- 精确的分支预测(>98%准确率)

- 动态指令窗口调整技术

-

电压/频率域精细化分割

- 现代低功耗CPU包含20+个独立电压域

- 毫秒级DVFS响应时间

- AMD Zen 5c的Per-Core Boost技术

-

近似计算技术

- 可配置精度浮点单元

- 关键路径动态松弛技术

3 系统级功耗管理

-

AI驱动的功耗预测

- 基于LSTM负载预测的预调节

- 苹果M5的神经功耗控制器

-

异构计算任务卸载

- 专用NPU处理AI负载(能效提升10-100倍)

- 高通Hexagon 780的矩阵扩展引擎

-

内存子系统优化

- 3D堆叠SRAM近存计算

- 非易失性内存的混合使用

性能平衡策略

1 动态性能调节机制

2025年主流低功耗CPU采用三级性能调节:

-

纳秒级调节

- 指令级门控时钟

- 无效操作抑制

-

微秒级调节

- 核心部分功能单元动态启停

- 缓存bank级功耗管理

-

毫秒级调节

- DVFS电压频率调整

- 核心睡眠状态转换

2 能效-性能Pareto优化

通过以下方法实现最佳能效曲线:

-

工作点自动追踪

- 实时监测IPC与功耗关系

- ARM DSU-110的动态工作点算法

-

温度感知调度

- 考虑热累积效应的任务分配

- Intel Thread Director 3.0技术

-

QoS约束下的能效优化

- 保证最低性能要求的功耗最小化

- 谷歌Tensor G4的QoS控制器

未来发展趋势

基于2025年技术路线图,低功耗CPU将呈现以下发展方向:

-

光子-电子混合计算

- 光互连降低芯片内通信功耗

- 预计2027年实现商用

-

常温超导计算

- 超导逻辑电路零电阻特性

- IBM等公司实验室阶段研究

-

神经形态计算

- 事件驱动型异步架构

- Intel Loihi 3的脉冲神经网络

-

量子-经典混合架构

- 特定算法卸载到量子处理单元

- 谷歌Sycamore 3代处理器

2025年的低功耗CPU技术已从单纯的功耗降低发展为智能化的能效优化体系,通过制程进步、架构创新和系统级协同设计,现代低功耗CPU能够在mW级至W级的功耗范围内提供媲美传统高性能核心的计算能力,随着新材料、新器件和新计算范式的引入,能效比有望继续呈指数级提升,推动计算设备向更小型化、更智能化和更普适化的方向发展。

本文由蹇长星于2025-09-17发表在笙亿网络策划,如有疑问,请联系我们。

本文链接:http://pro.xlisi.cn/wenda/26763.html